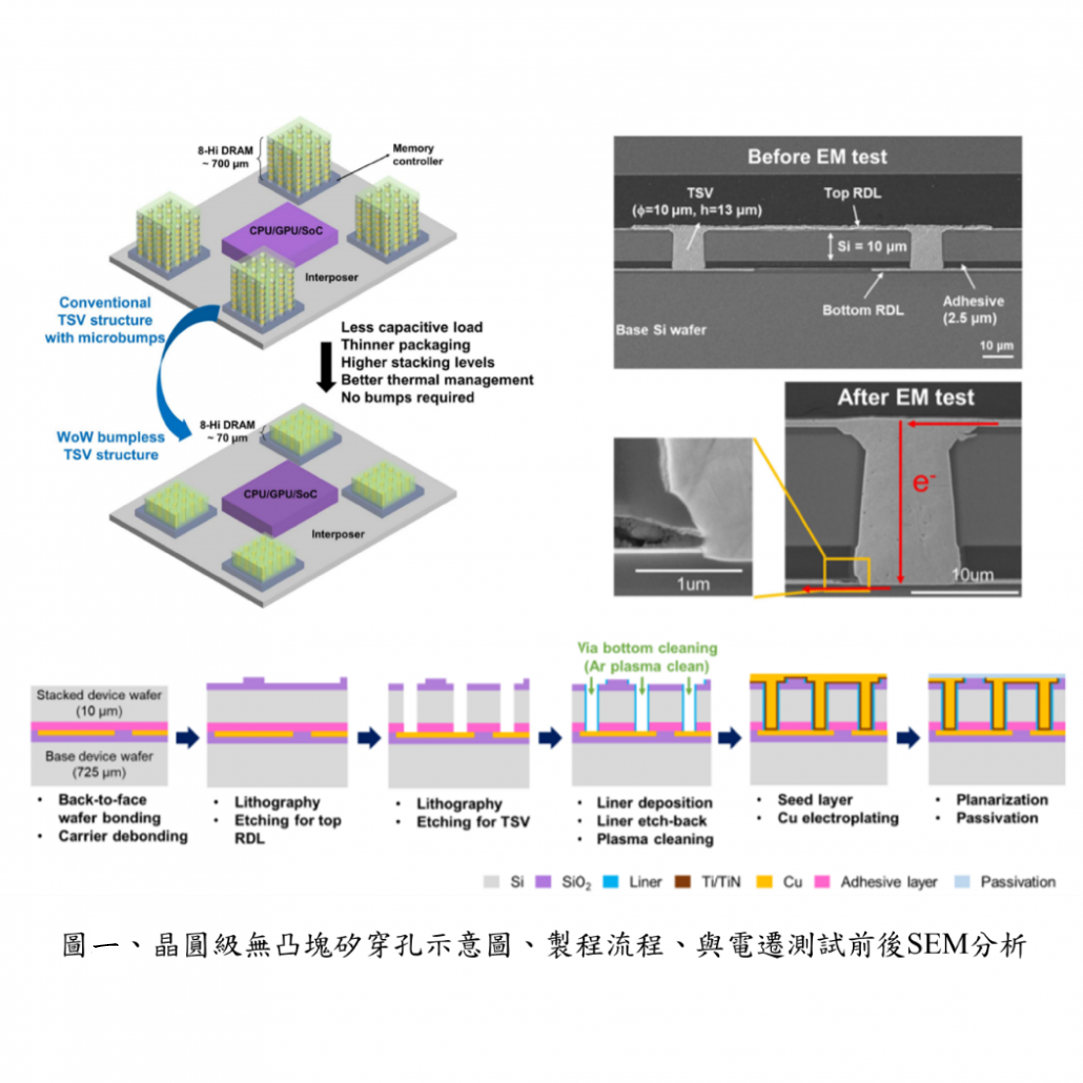

晶圓級無凸塊矽穿孔

在三維積體電路的垂直整合架構中,矽穿孔(TSV)技術為其中關鍵,能藉由垂直的矽穿孔連接上下層的電晶體與電路,較傳統打線封裝可以大幅提升晶片間傳輸效率並降低功耗。而矽穿孔技術有著如凸塊微縮、熱膨脹係數不匹配、較低抗電遷以及熱傳導等問題,團隊展示了晶圓級無凸塊矽穿孔架構,配合穿孔底部清潔技術,可以改善TSV架構的電性、電遷移以及TCT、HAST可靠度等測試結果,如圖一所示。

此方案採用的晶圓級封裝技術能提供高封裝產出,具高度業界可行性,另外無凸塊的架構能提供更輕薄的堆疊結構,適用於像是高頻寬記憶體等多層堆疊應用,團隊以新的電路模型能更有效率的模擬無凸塊結構於多層堆疊架構電性,展示團隊的穿孔底部清潔技術在多層堆疊時可以有效減少訊號的傳輸損耗。