積層型三維積體電路

在積層型三維積體電路中,不同的主動層是以連續製程實現三維整合,並用超高密度的層間穿孔連接上下層電路,得以提升傳輸效率、降低功耗、以及減少元件體積。而影響積層型三維積體電路效能的關鍵在於處理多層主動層連續製程的熱影響,以避免其對下層的電晶體或電路造成損耗,另外,連續製程用到多晶半導體中,像是多晶矽的隨機晶界亦會降低此技術的良率。

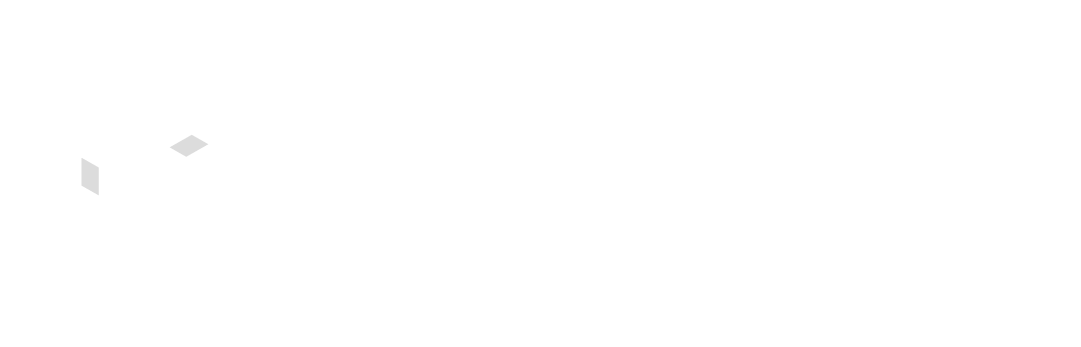

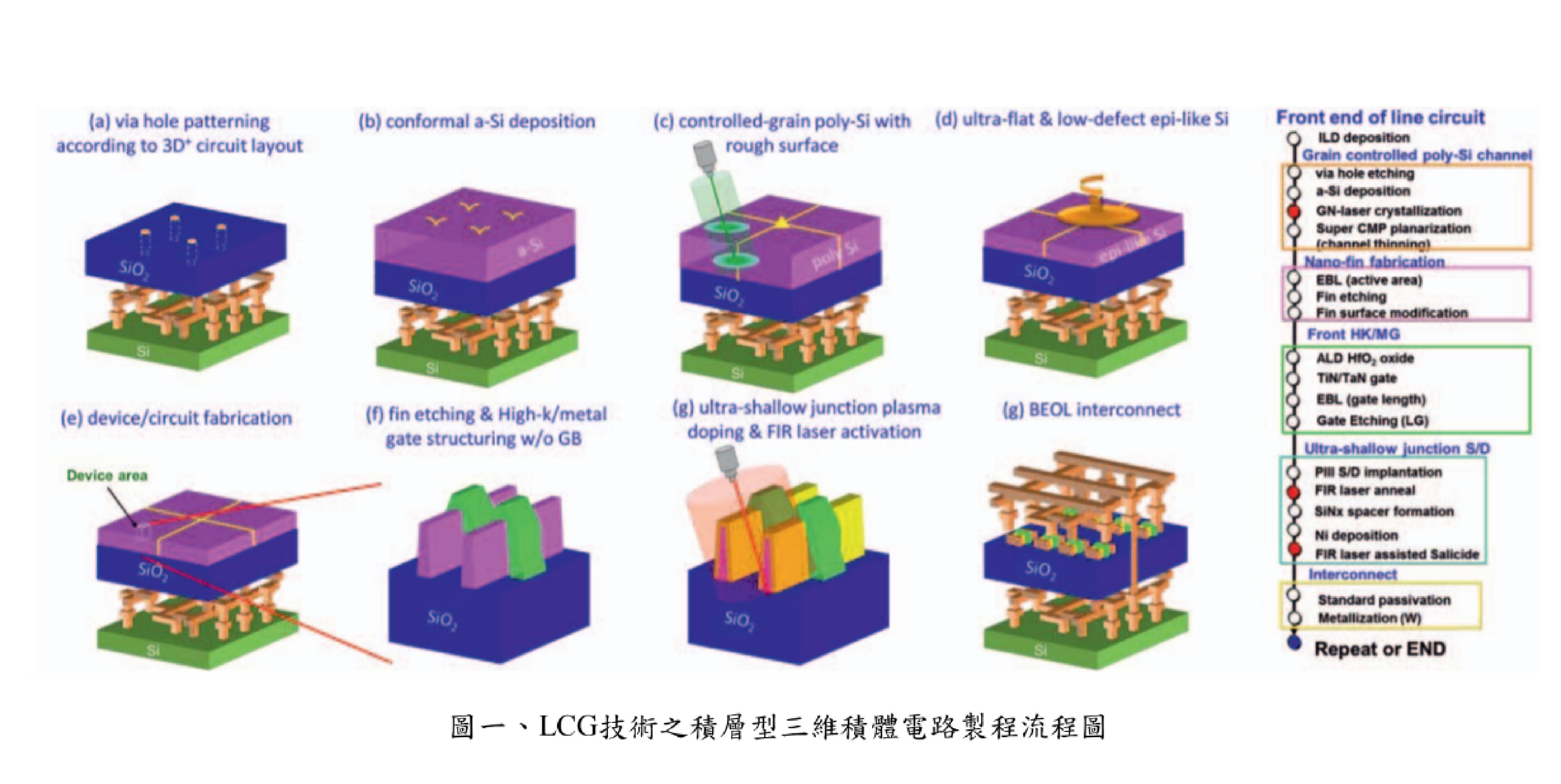

團隊開發BEOL location-controlled grain (LCG)的技術,使用脈衝雷射退火技術在被控制的熱預算下製程積層型三維鰭式場效電晶體電路,此技術流程如圖一所示,其中的關鍵步驟是在層間介電質蝕刻出冷卻孔,提供選擇性冷卻與晶種,在施加脈衝雷射下讓單晶出現於冷卻孔頂部進而形成單晶矽陣列,此外,透過熱分布模擬可驗證脈衝雷射退火時,底層的電晶體與電路皆低於後段製程所能容忍之溫度(400 ℃),如圖二所示。

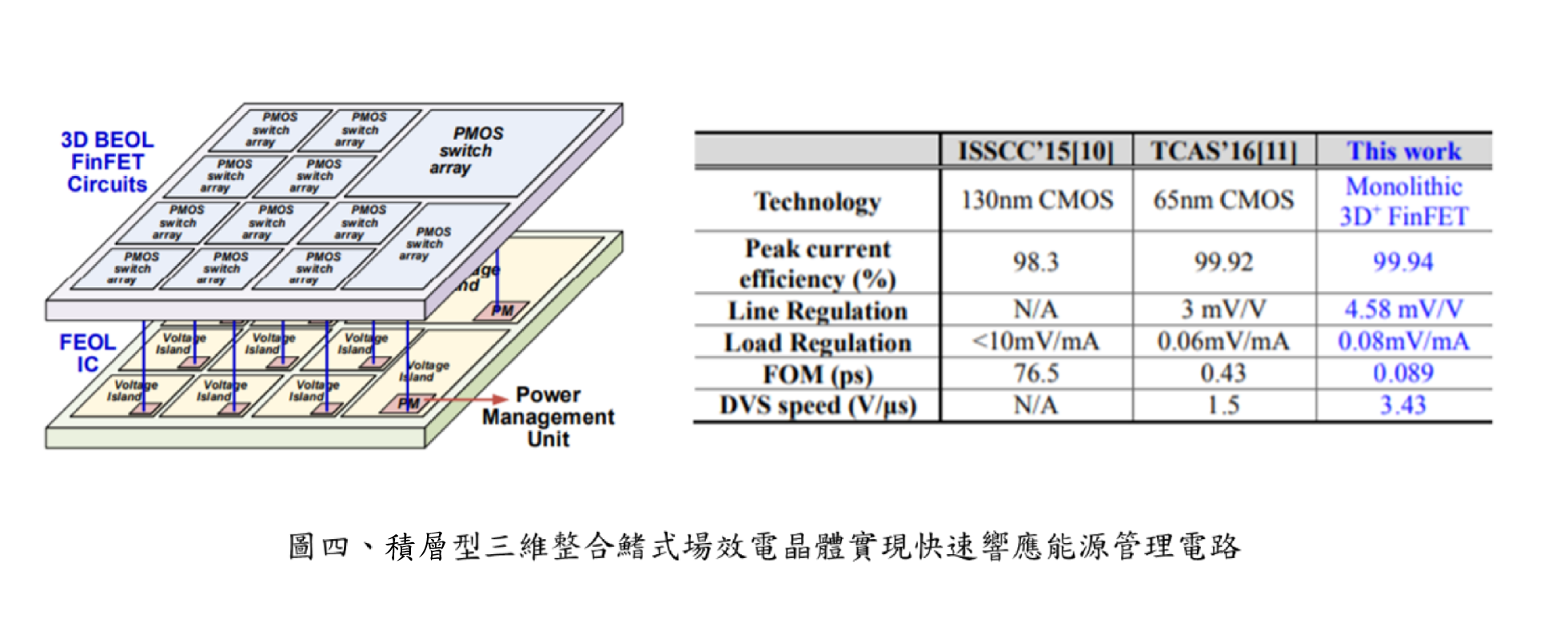

團隊接下來的研究提出結合冷卻孔、氮化矽介面、網狀圖案非晶矽島與覆蓋氧化層的結構以改進LCG技術,在雷射退火後可達成面積大小為2.56 μm²的單晶矽,如圖三所示。團隊基於此改良的LCG技術進而製程了積層型三維整合的鰭式場效電晶體,實現快速響應能源管理電路,並展示比其他二維調節器更佳的響應時間與理論FOM,如圖四所示。

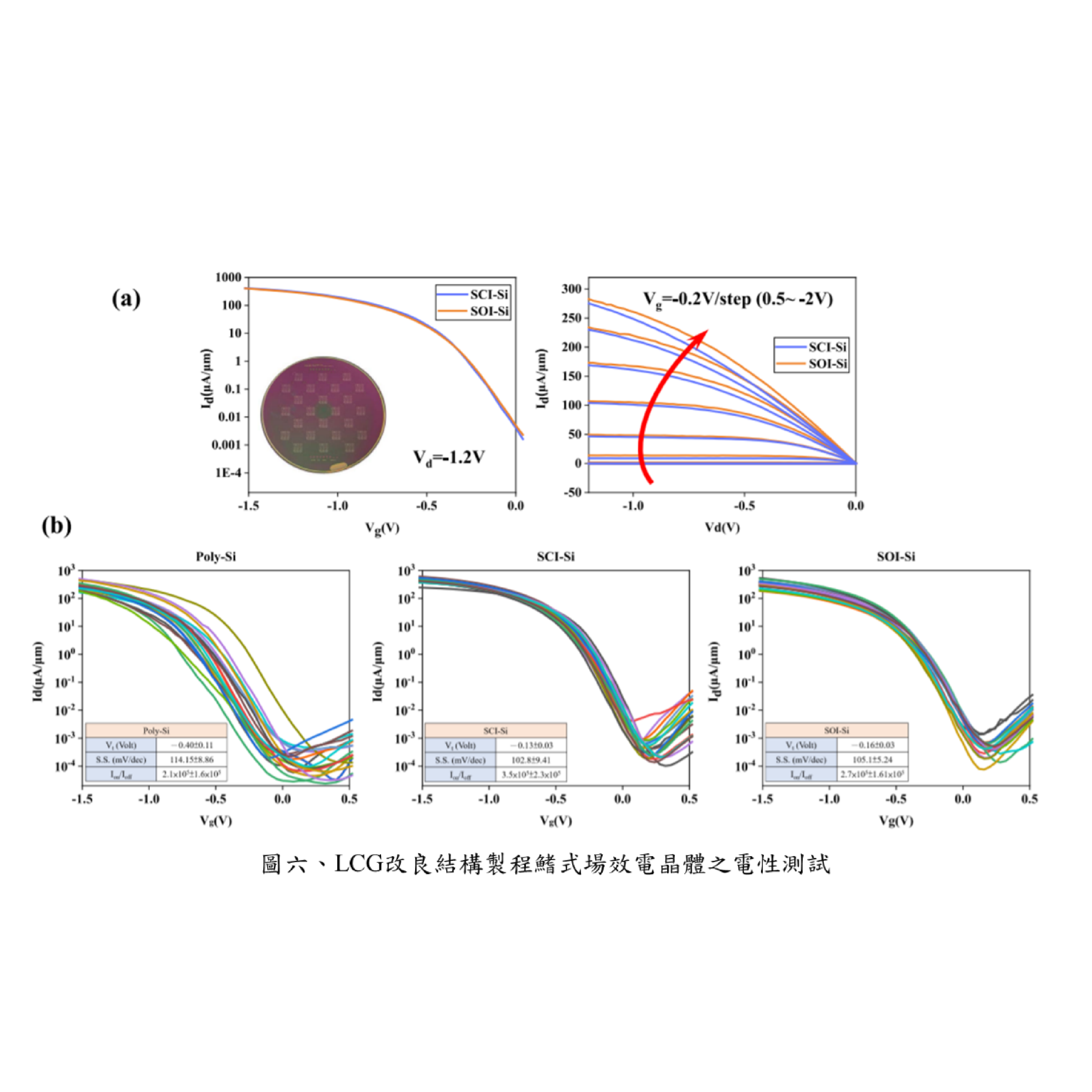

在2021年的發表中,團隊指出藉由在網狀圖案非晶矽島上覆蓋一層氮化矽,並施以雷射結晶,單晶矽陣列的品質能更進一步提升,此結果經由SECCO Etch、HREM、TEM、EBSD等分析作完整的驗證,如圖五所示,同時,團隊也以此技術製程40 nm鰭式場效電晶體於單晶矽陣列中,並展示了其優異的電性效能足以匹配於以市售SOI晶圓製程的鰭式場效電晶體,如圖六所示。