Novel Low-Warpage Hyper RDL (HRDL) Interposer

Recently, there has been a significant focus on advancing high-performance organic dielectric-based Redistribution Layer (RDL) Interposer applications for electronic chips and systems. To meet design requirements, these interposers must support fine pitch, high density, a high layer count, low RC delay, and the capability to embed silicon chips. Nevertheless, stacking RDL structures with a high layer count using conventional semi-additive processes (SAP) presents significant challenges due to worsening surface topography and warpage as the number of layers increases. Additionally, alignment precision in fine-pitch lithography processes becomes increasingly constrained. Consequently, developing advanced technologies for RDL interposer fabrication has become crucial to address these issues and meet industry demands.

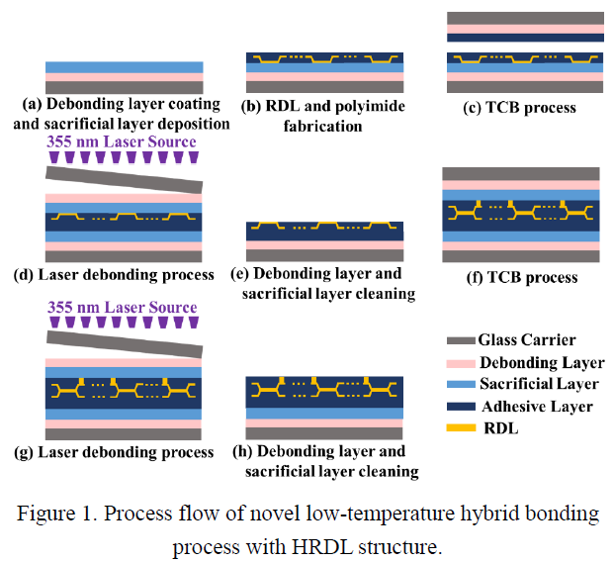

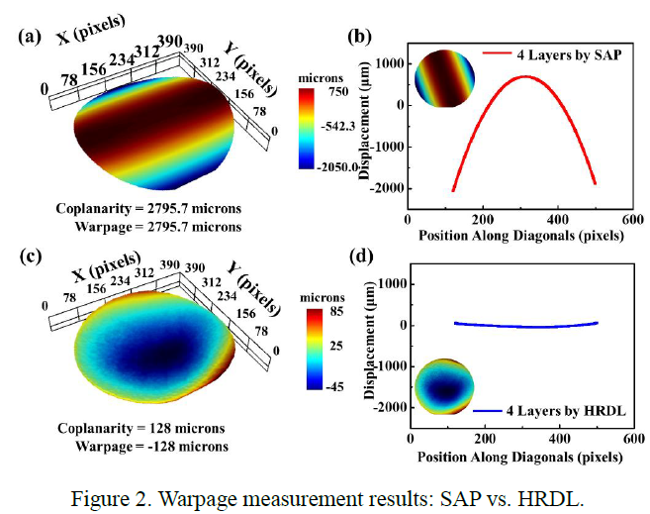

In our team, a novel approach called hyper RDL (HRDL) is proposed, with the proposed HRDL process flow shown in Figure 1. In this study, we demonstrate the removal of carrier wafers through the laser debonding process, and the HRDL structure was performed through the utilization of low-temperature hybrid bonding technology. Figure 2 provides a comparison between the conventional semi-additive process (SAP RDL) method and the novel Hyper RDL (HRDL) method. By transitioning from the SAP RDL process flow to the HRDL process flow, the warpage can be significantly reduced from 2795.7 μm (~2.8 mm) to only 128 μm (~0.1 mm). This significant warpage reduction provides promising evidence of the significant warpage improvement achievable with the HRDL method, which is highly beneficial for high layer count RDL manufacturing yield and fine pitch RDL fabrication.

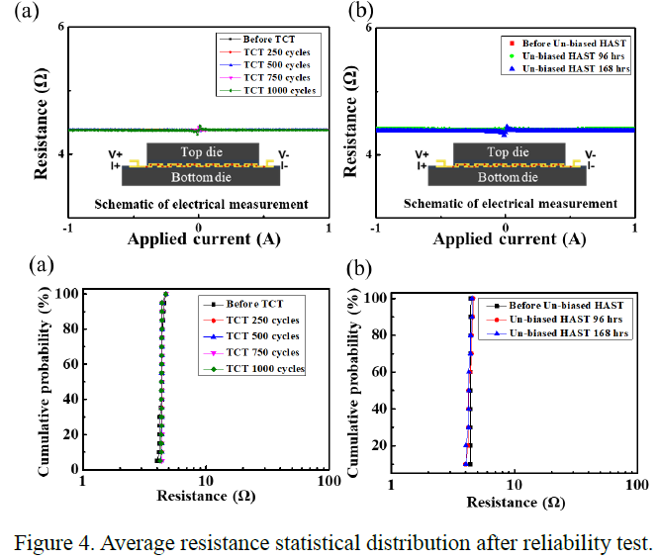

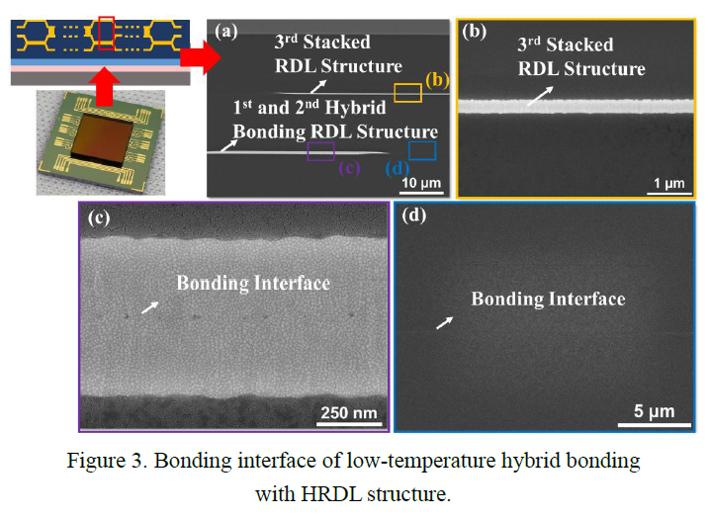

A three-layer-stacked RDL structure fabricated using the HRDL process is presented in Figure 3. SEM image shows the outstanding metal and polyimide bonding interface. Figure 4(a) shows the average resistance statistical distribution after the thermal cycling test (TCT) from the initial state to 1000 cycles, with the temperature cycling between -55℃ and 125℃. Figure 4(b) shows after un-biased highly accelerated stress test (un-biased HAST) from the initial state to 168 hours, performed at a constant temperature of 130℃ with 85% relative humidity. Both the thermal cycling of 1000 cycles and the un-biased highly accelerated stress test of 168 hours showed less than 1.5% change in electrical resistance. The HRDL process flow is designed to ensure reasonable running costs without the need for polymer chemical mechanical planarization (CMP). This innovative approach leads to a low-warpage RDL interposer platform for advanced packaging applications.